# Prediction of Interconnect Adjacency Distribution: Derivation, Validation, and Applications

Payman Zarkesh-Ha, Ken Doniger, William Loh, and Peter Bendix

LSI Logic Corporation Interconnect Modeling Group February 14, 2004

Slide 1 SLIP 2004

#### **Outline**

- \* Motivation

- \* Interconnect Adjacency Model

- \* Derivation

- \* Validation

- \* Applications

- \* Conclusion

Slide 2 SLIP 2004

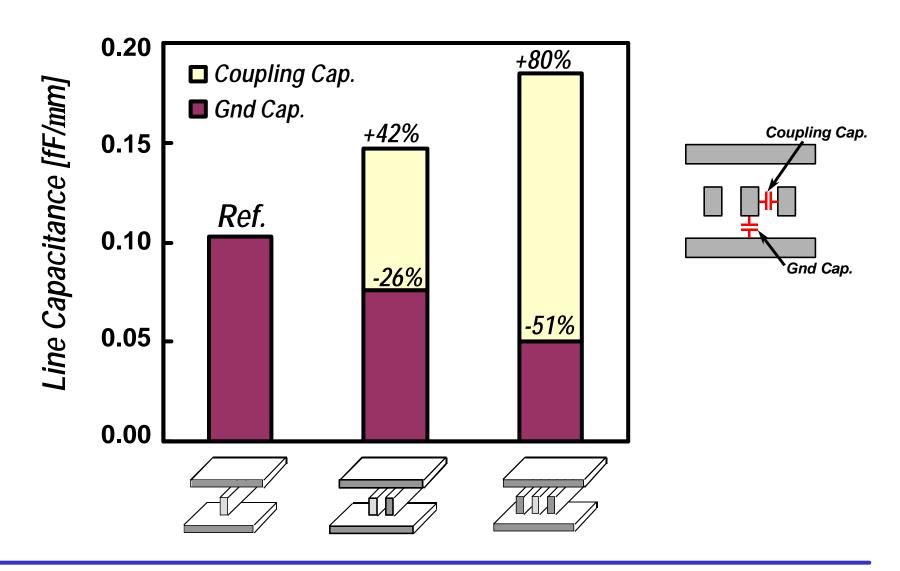

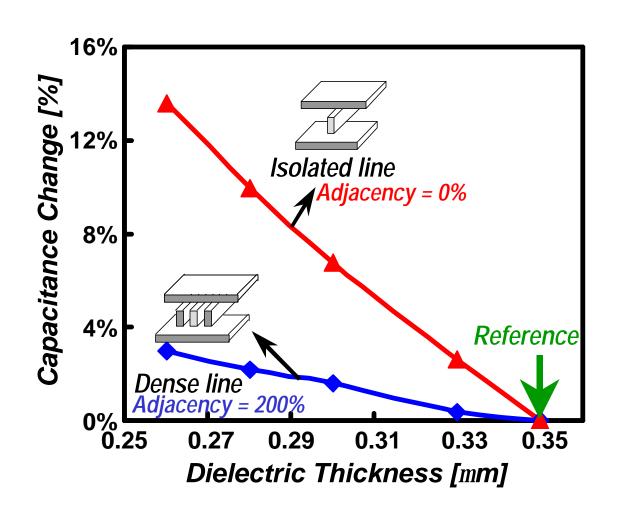

## Effect of Geometry on Capacitance

Slide 3 SLIP 2004

#### **Motivation**

\* How to choose the geometry for system level modeling of interconnect capacitance:

- \* A real system is a mix of many cases.

- \* A statistical approach is required to predict the capacitance distribution more realistically.

- \* We will derive the interconnect geometry distribution that produces circuit variations.

Slide 4

#### **Outline**

- \* Motivation

- \* Interconnect Adjacency Model

- \* Derivation

- \* Validation

- \* Applications

- \* Conclusion

Slide 5 SLIP 2004

## **Assumptions**

- \* Wire placement in a random logic network is complex and irregular enough to be modeled by a probability distribution involving "coin flipping".

- \* Average channel utilization, p, is known.

Slide 6 SLIP 2004

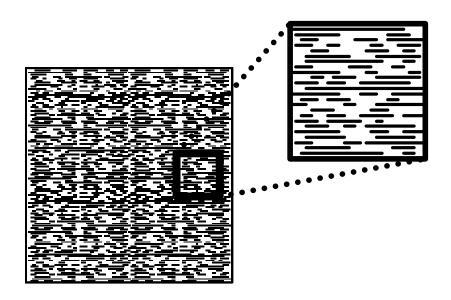

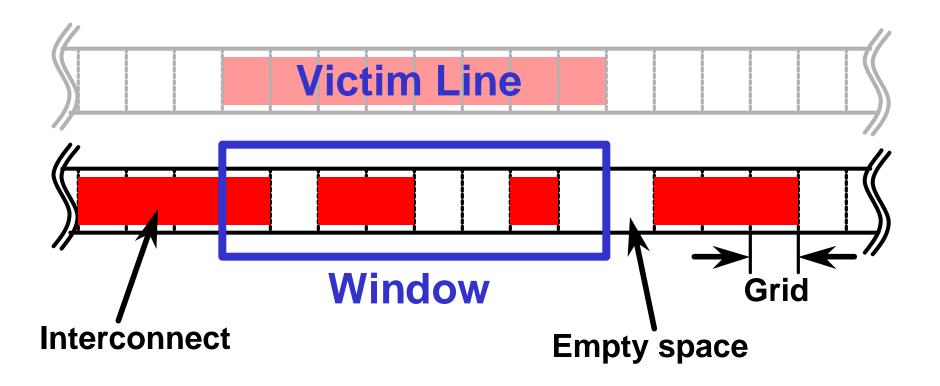

## What is Adjacency?

Interconnect adjacency is the fractional length of an interconnect that possesses neighbors at minimum spacing.

Slide 7 SLIP 2004

### **Definitions**

Slide 8 SLIP 2004

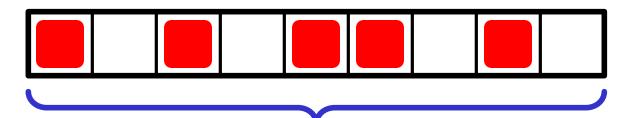

## Simple Case: Unit Length System

#### Window of size n=9

$$f(k) = \frac{e}{k!} \frac{n!}{k!(n-k)!} \frac{\ddot{0}}{\dot{p}} p^{k} (1-p)^{n-k}$$

Bernoulli Distribution

n = total number of grids

k = number of filled grids

p = probability of filling

## Realistic System

- \* Wires are random length (not all unit length).

- **★** Window size, *n*, is not constant anymore.

- **\*** Wires may cross window boundaries.

Derivation details available in the paper.

Slide 10 SLIP 2004

## Model Input

- \* Average channel utilization, p.

- \* Minimum and maximum segment length.

- \* Grid size.

- \* Segment length distribution.

- Can be derived from Rent's rule by partitioning.

- Can be fit empirically.

Slide 11 SLIP 2004

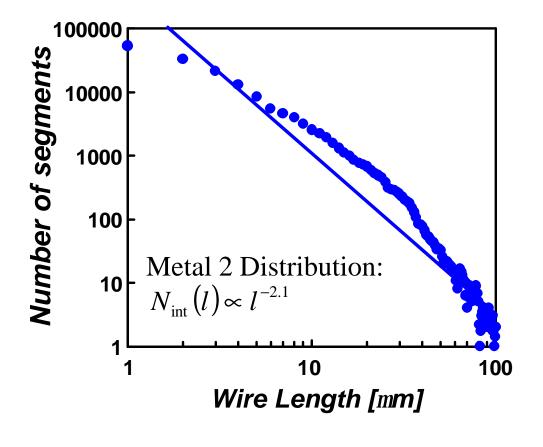

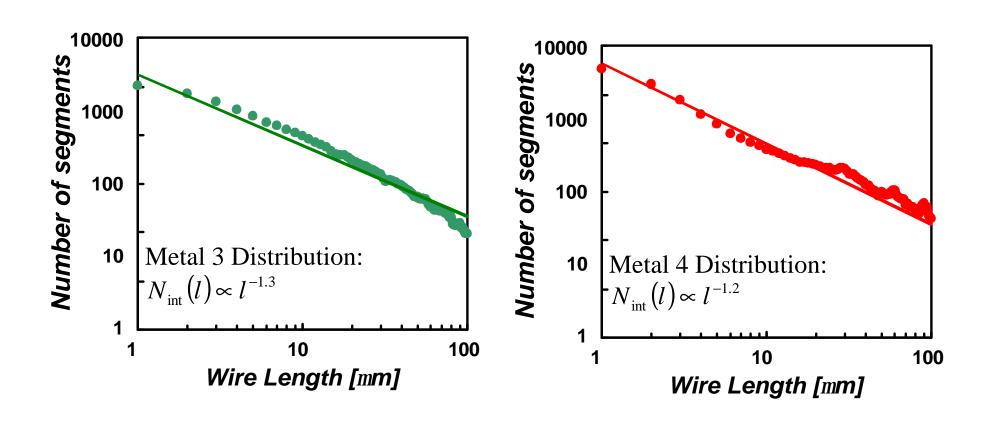

## M2 Segment Length Distribution

Technology = 130nm

Metal layer = M2

Min wire length = 1.0 mm

Max wire length = 100 mm

**Slide 12** SLIP 2004

## Other Segment Length Distribution

Slide 13 SLIP 2004

#### **Outline**

- \* Motivation

- \* Interconnect Adjacency Model

- \* Derivation

- \* Validation

- \* Applications

- \* Conclusion

Slide 14 SLIP 2004

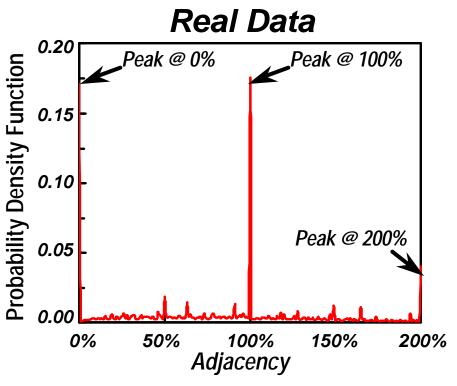

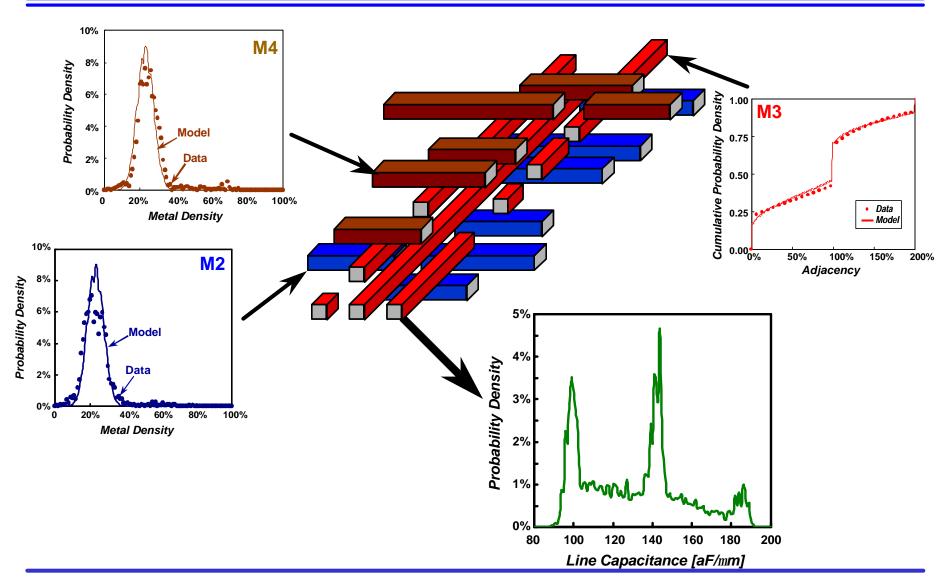

## Comparison with Actual Data PDF

Metal layer = M2 Technology = 130 nm Channel utilization = 40% Min wire length = 1.0 mm Max wire length = 100 mm Grid size = 0.01 mm

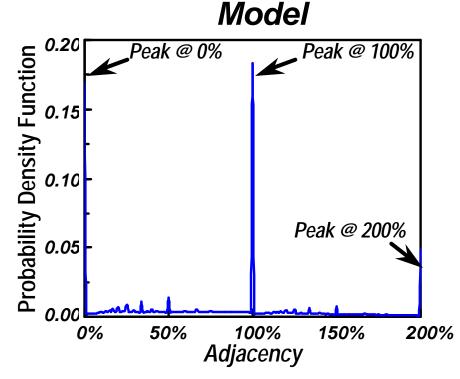

## Comparison with Actual Data CDF

Slide 16 SLIP 2004

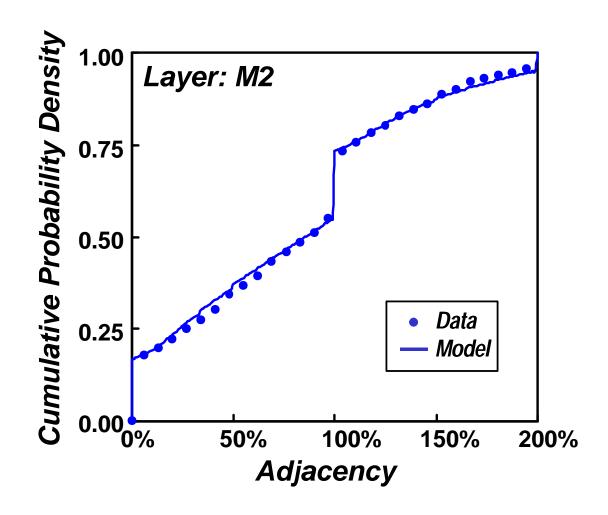

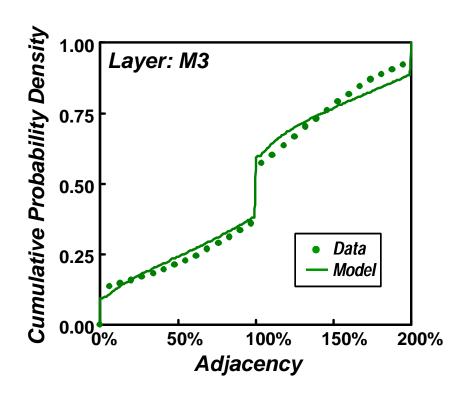

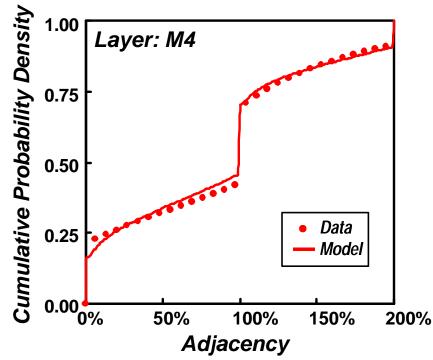

## Comparison with Actual Data CDF

Metal layer = M3

Channel utilization = 50%

Gate pitch = 1.0 mm

Max wire length = 150 mm

Grid size = 0.01 mm

Metal layer = M4

Channel utilization = 42%

Gate pitch = 1.0 mm

Max wire length = 150 mm

Grid size = 0.01 mm

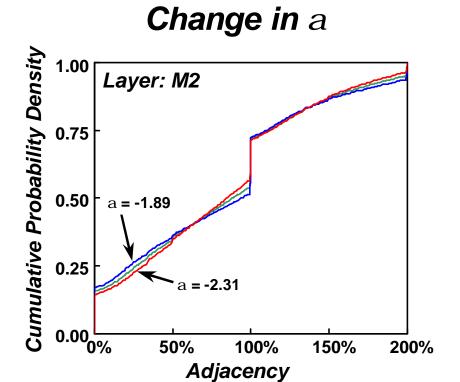

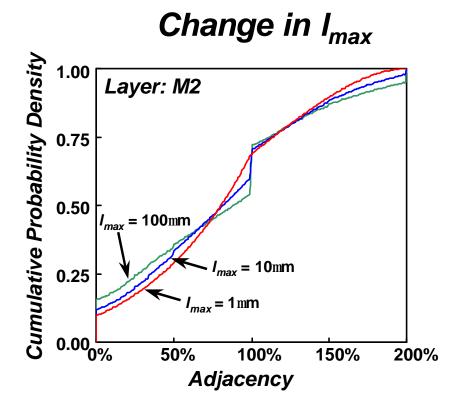

## Sensitivity to Length Distribution

Slide 18 SLIP 2004

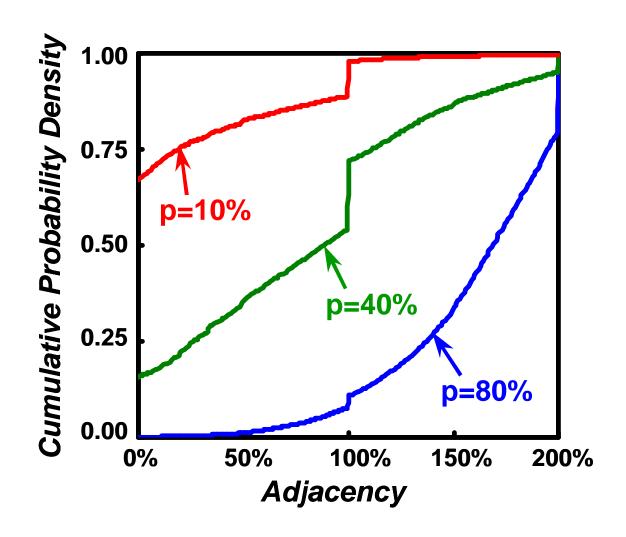

## Adjacency Distribution Change with p

Slide 19 SLIP 2004

#### **Outline**

- \* Motivation

- \* Interconnect Adjacency Model

- \* Derivation

- \* Validation

- \* Applications

- \* Conclusion

Slide 20 SLIP 2004

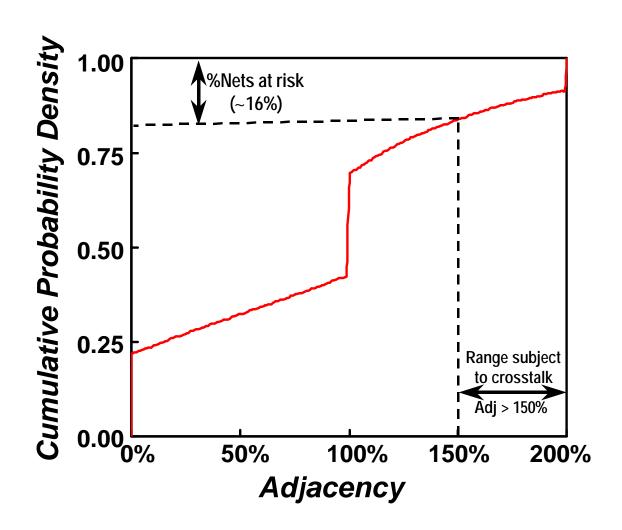

## Statistical Crosstalk Analysis

Slide 21 SLIP 2004

## Sensitivity Analysis

Slide 22 SLIP 2004

#### Interconnect Statistical Reference

Slide 23 SLIP 2004

#### **Outline**

- \* Motivation

- \* Interconnect Adjacency Model

- \* Derivation

- \* Validation

- \* Applications

- \* Conclusion

Slide 24 SLIP 2004

#### **Conclusions**

- \* Compact model for Interconnect Adjacency Distribution for random logic networks is derived.

- \* The model uses only system level generic parameters such as segment length distribution and channel utilization. This enables us to predict future system level performance.

- \* Comparison to product data confirms the accuracy of the model.

- \* Some possible applications of the adjacency are proposed.

Slide 25 SLIP 2004

## Acknowledgement

We acknowledge Ralph Iverson from Magma Design Automation for his generous support in the extraction of the real data.

Slide 26 SLIP 2004