# Constant Impedance Scaling Paradigm for Interconnect Synthesis

J. Balachandran, S. Brebels, G. Carchon, M. Kuijk<sup>1</sup>, W. De Raedt, B. Nauwelaers<sup>2</sup>, E. Beyne

> <sup>1</sup>Vrije Universiteit Brussel, Belgium <sup>2</sup>Katholieke Universiteit Leuven, Belgium

> > SLIP 2006 4-5<sup>th</sup> March Munich, Germany

# Introduction

- Global interconnects are *performance limiters* in nano-CMOS regimes

- Billion transistor + Integration densities

- GHz range clock frequencies

• "Computer Architecture is all about Interconnects" — Bill Dally, Stanford

- Need for proper (global) interconnect design and optimization

- Application Independent

- Interconnect stack technology development

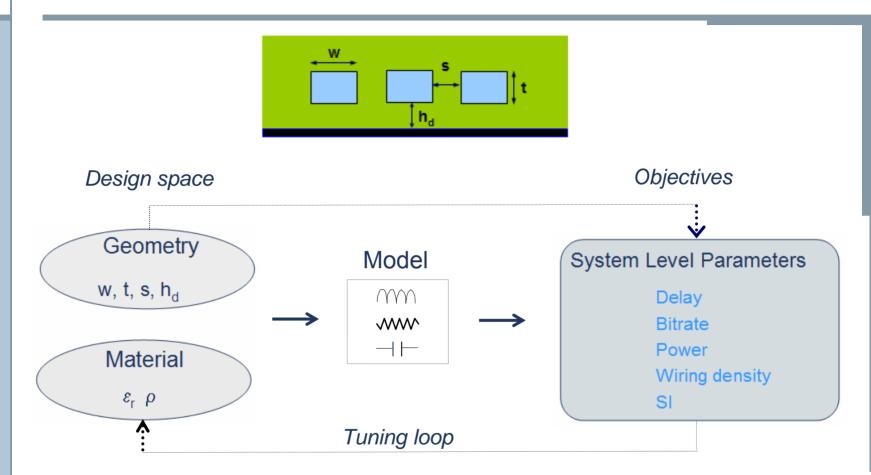

### **Interconnect Design Loop**

- Numerous possibilities in the design space

- Systematic Design ?

- $\rightarrow$  Constant Impedance Scaling

- Introduction

- Concept

- Methodology

- Design strategies

- Conclusion

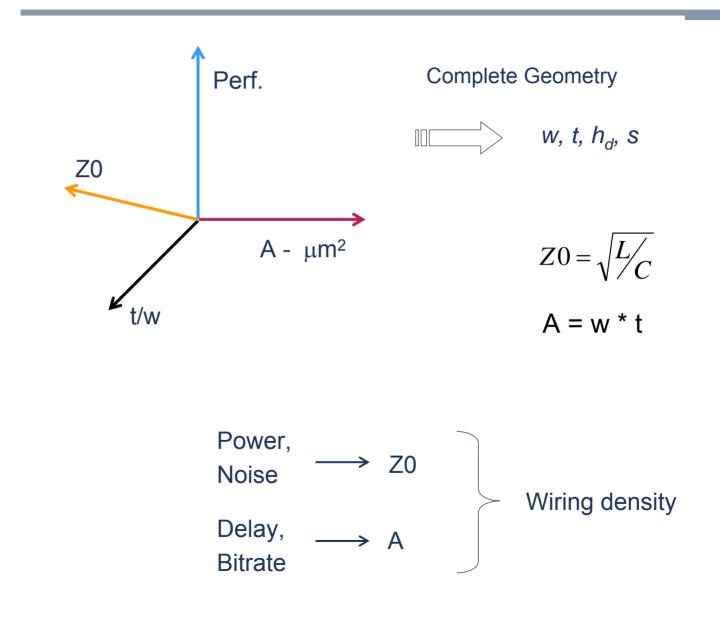

# **Interconnect Design Space Abstraction**

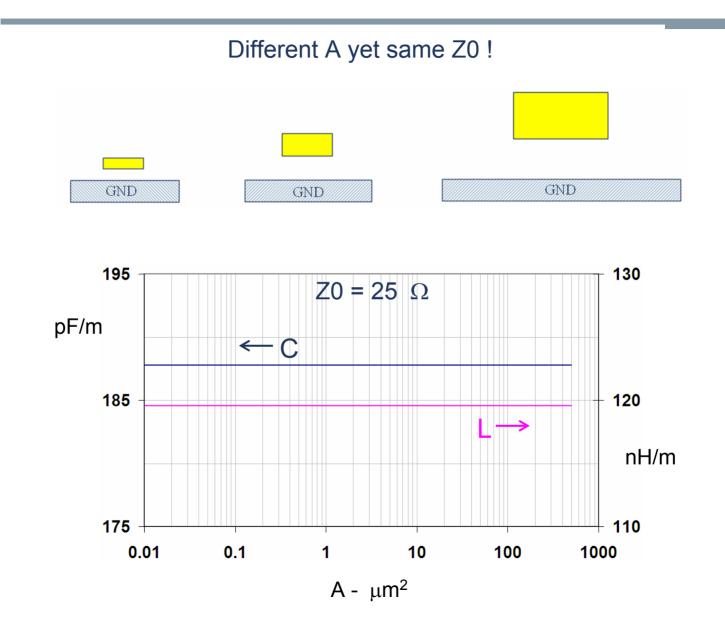

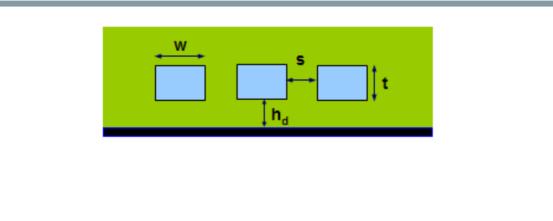

- R depends on the cross-sectional area (A)

- Absolute quantity

- Scaling variable

- L and C depends on spacing between adjacent lines

- Relative quantity

- Impedance Abstraction

$$Z0 = \sqrt{\frac{L}{C}}$$

# L and C can be fixed independent of A

### **Interconnect Design Space Abstraction**

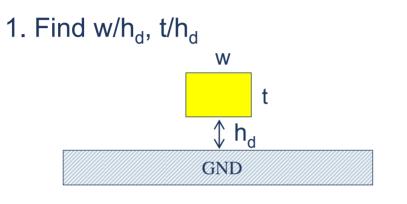

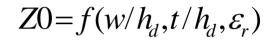

# **Design Methodology – Fix Design Ratios**

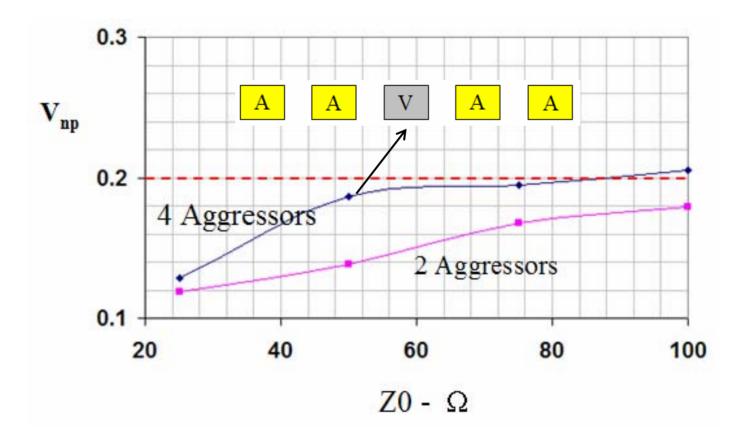

Xtalk <= 20% VDD Impedance unchanged Weak coupling

#### 2. Find s/h<sub>d</sub>

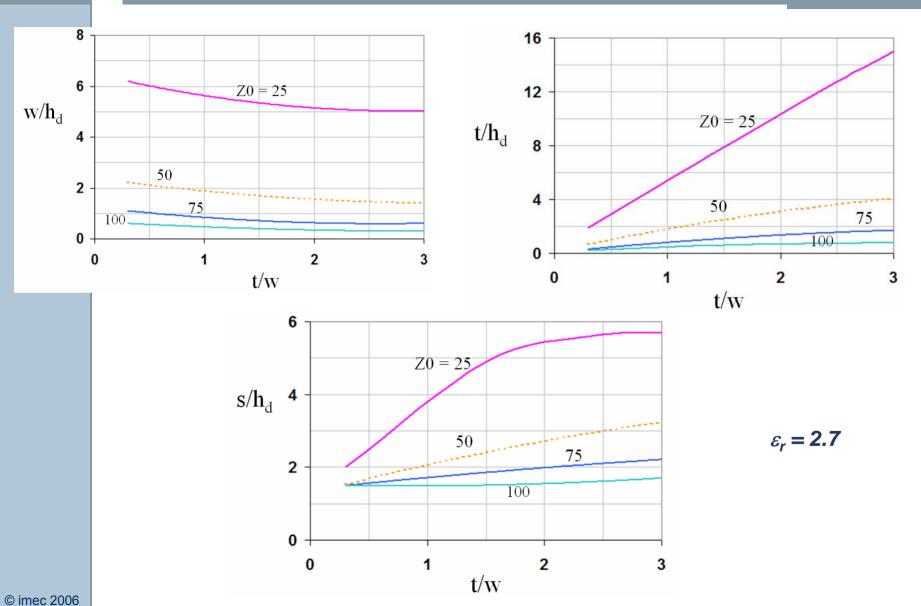

# **Design Ratios for different impedances**

9

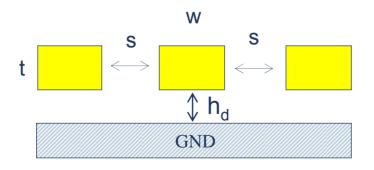

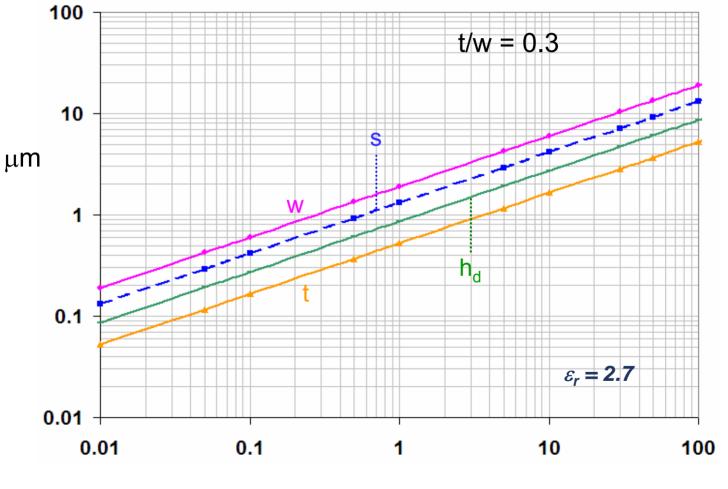

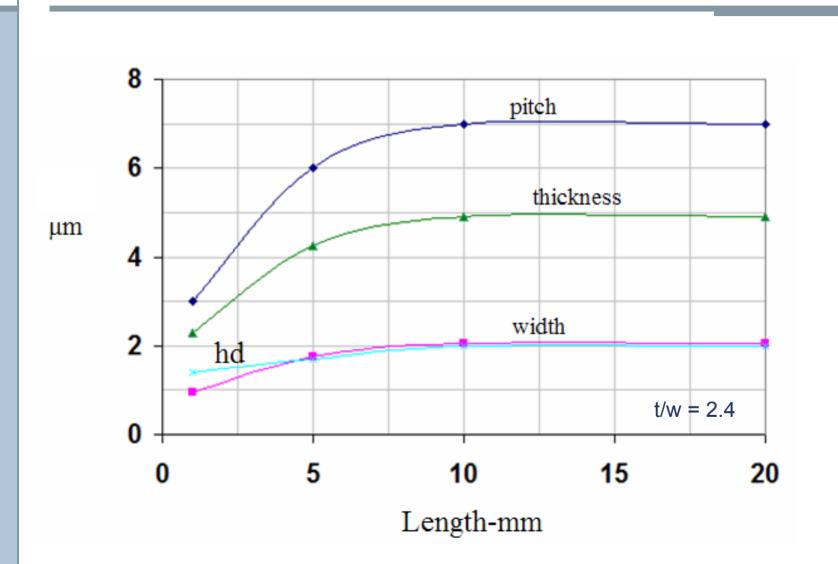

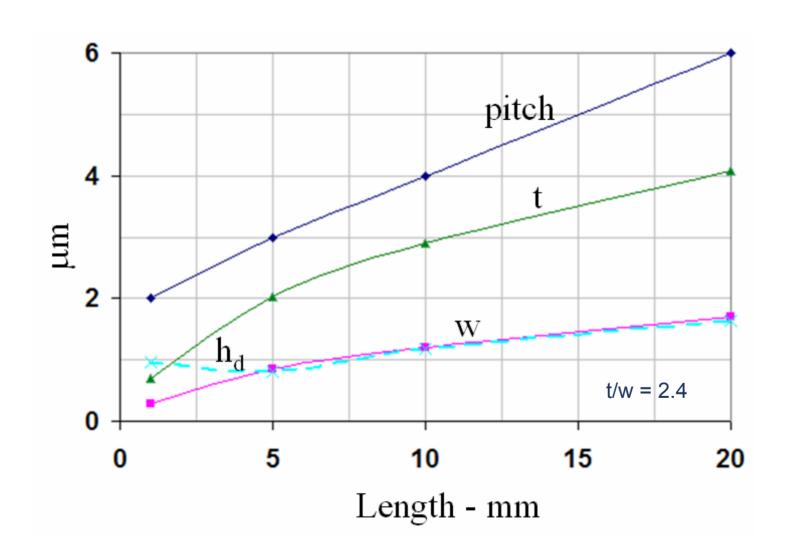

### Given Z0 and A Wire Geometry is fixed

#### Given t/w

$$Z0 = f(w/h_d, t/h_d, s/h_d, \varepsilon_r)$$

$$ar_1 = w/h_d$$

$$ar_2 = t/h_d$$

$$ar_3 = s/h_d$$

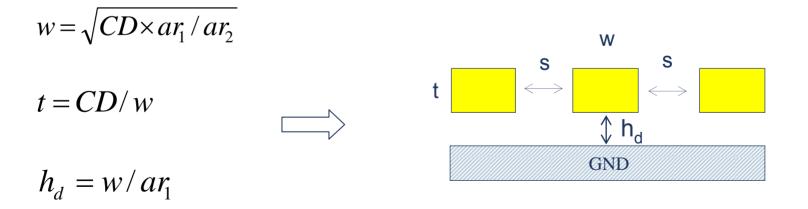

# Wire Geometry Example: 50 $\Omega$

$CD - \mu m^2$

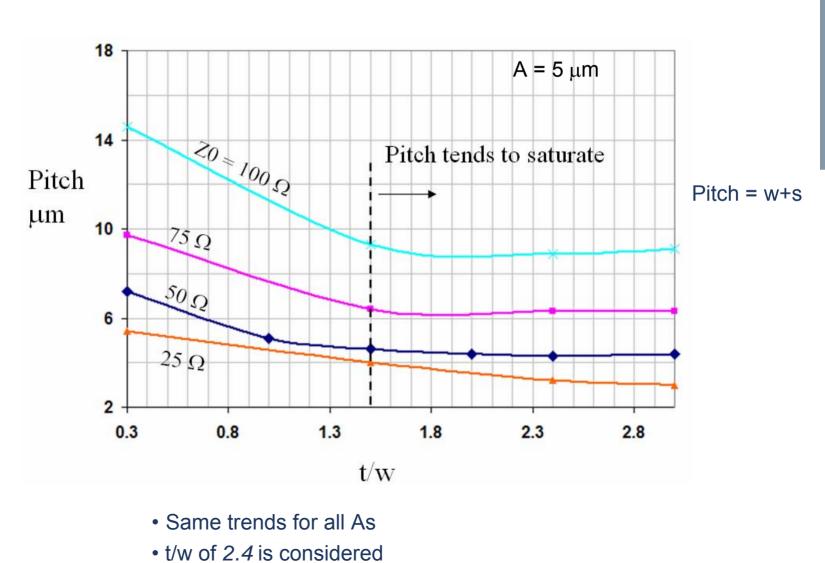

# t/w is chosen to minimize pitch

### **Interconnect Design Methodology**

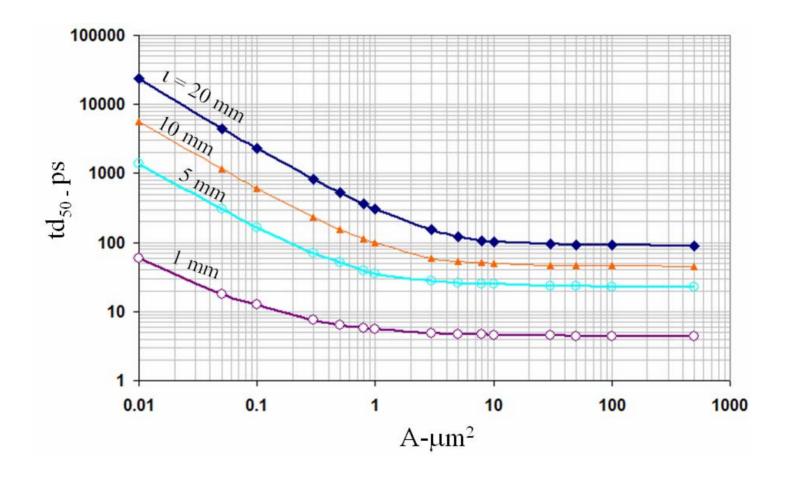

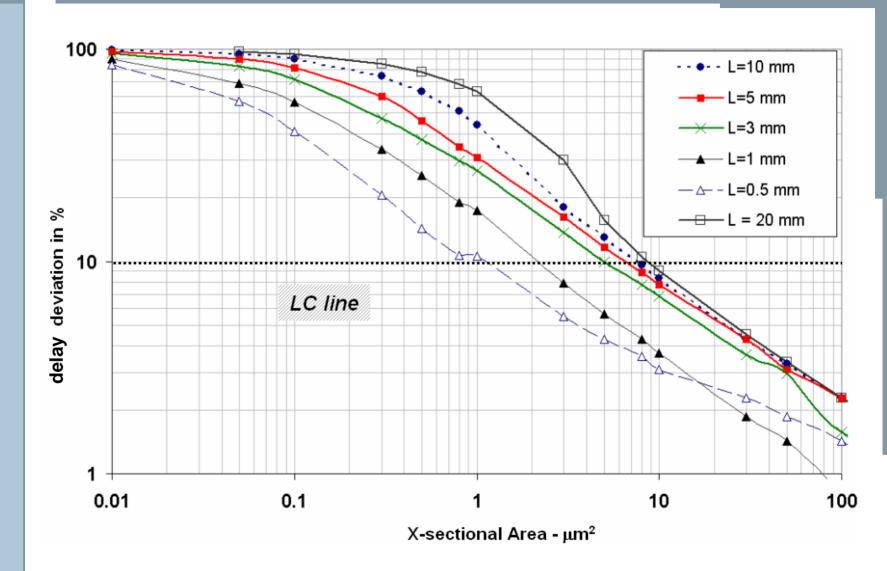

# Delay Characteristics of 50 $\Omega$ line

• Rich data set linking geometry and system parameter - delay

- -Tolerable xtalk up to 4 Aggressors

- Lower Z0 ; lesser Xtalk

- Vnp fairly independent of A

imec

**Outline**

- Introduction

- Concept

- Methodology

- Results

- Design strategies

- Conclusion

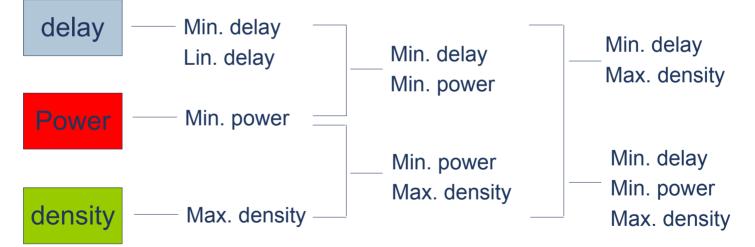

# **Interconnect design Strategies**

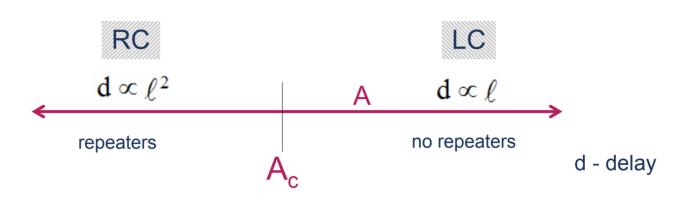

# Strategy: Min. delay

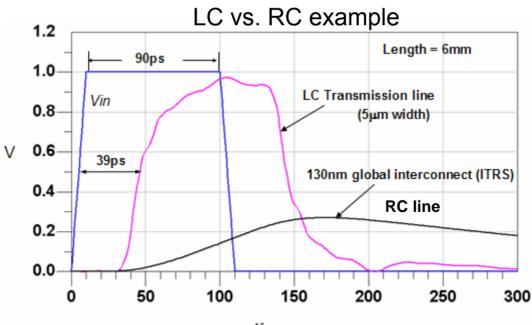

- Min. delay  $\rightarrow$  LC Transmission lines

- $-\sqrt{\varepsilon_r} / c_0 = \sqrt{LC}$

- Limited only by  $\epsilon_r$

- Near speed of light propagation

- Large A; delay independent of R

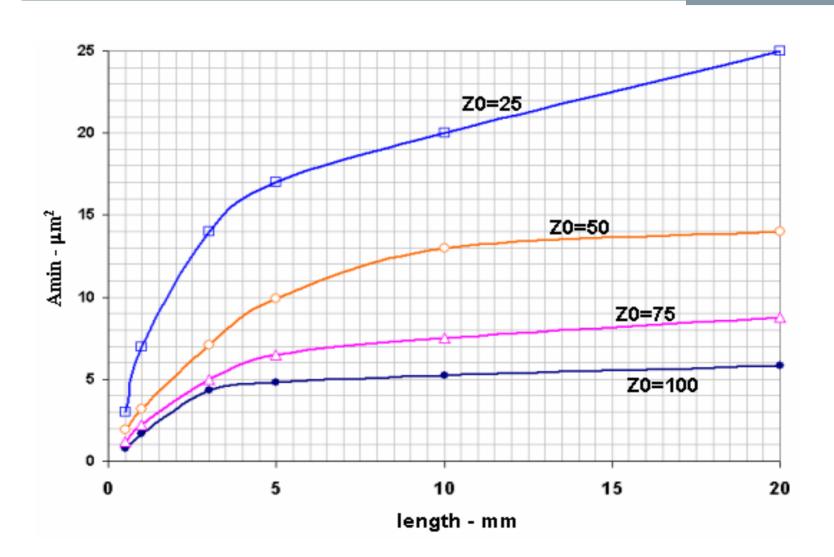

Find the <u>minimum interconnect</u> <u>X-sectional area (Amin)</u> required to achieve LC mode propagation for a given length ?

$$t \downarrow \bigcirc A = w.t$$

• LC mode propagation defined as delay with in 10% of Speed of light delay

#### Amin = 7.6um<sup>2</sup> for 10mm long 75 ohm line for min. delay

#### Amin decreases for increasing Z0

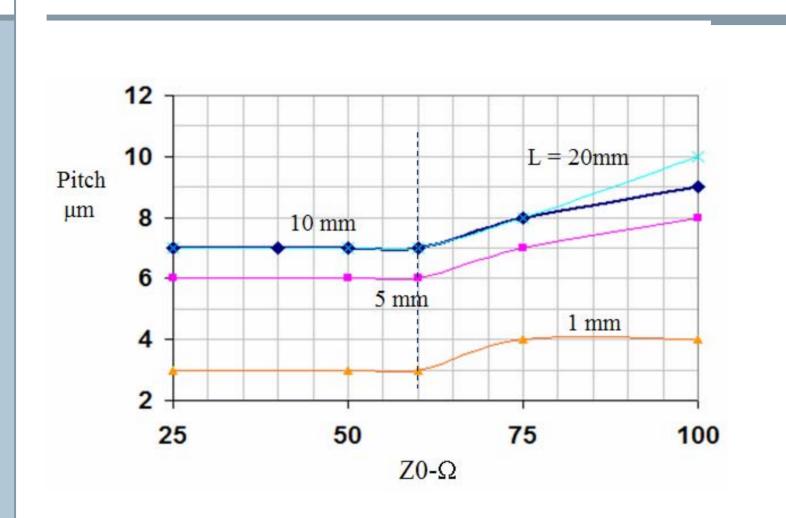

#### Pitch vs. Length under X-talk constraint

$60~\Omega$  - Optimal Z0 for Min. delay

#### **Optimal Geometry for LC Transmission lines**

# Design Strategy Repeater Less Line

# **Repeater less line**

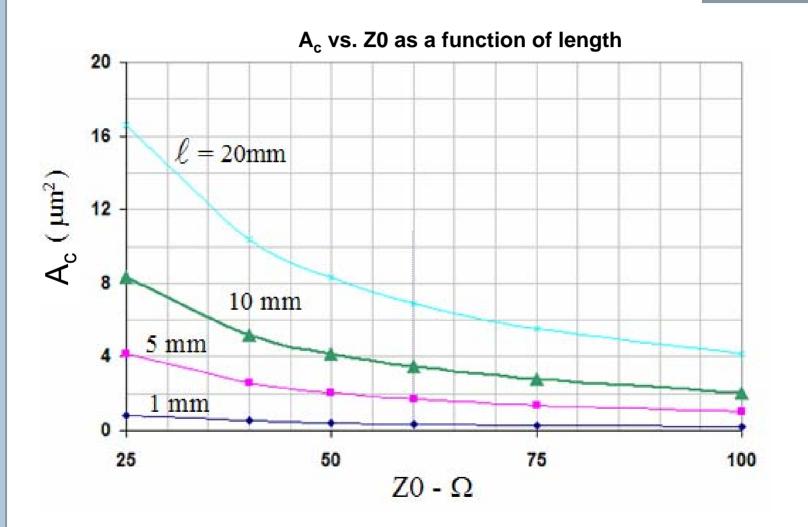

#### What is the RC-LC cutoff point $(A_c)$ ?

Equating RC and LC delays

$$A_{c} = \frac{1.2\rho\ell}{Z0}$$

### Ac decreases with Z0

• Optimal Z0 = 60  $\Omega$

# **Optimal Geometry for Repeater less line**

**Design Strategy**

Min. Delay Max. Wiring density

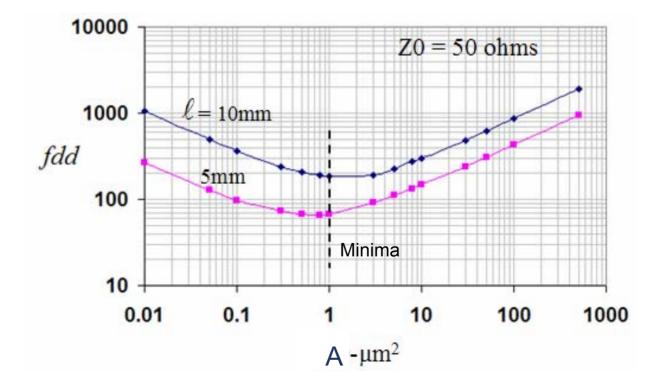

# Strategy: Min. delay, Max. Wiring density

Define figure of merit

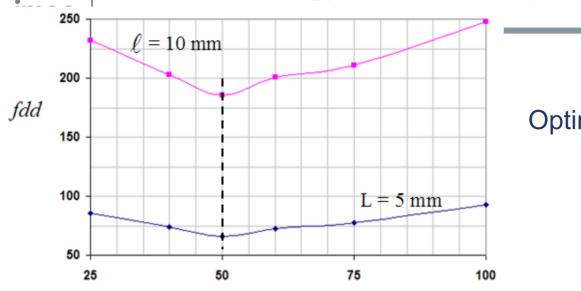

$$fdd = \min\left(\frac{delay}{density}\right) = \min(delay.pitch)$$

# Strategy: Min. delay, Max. Wiring density

**Z0-**Ω

Optimal Z0 =  $50\Omega$

Optimal Geometry for L = 10 mm $W = 0.65 \mu \text{m}$  $t = 1.55 \mu \text{m}$  $h_d = 0.44 \mu \text{m}$  $P = 2 \mu \text{m}$

**Design Strategy**

Min. Delay Min. Power Max. Wiring density

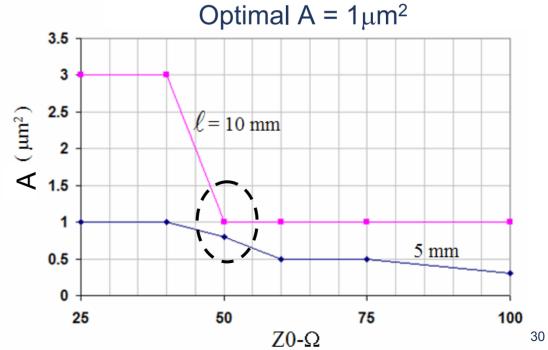

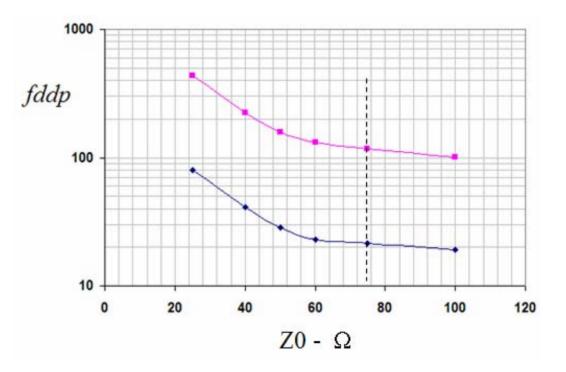

Define figure of merit

$$fddp = \min\left(\frac{delay \times C}{density}\right) = \min(delay \times pitch \times C)$$

• Optimal Z0 = **75**  $\Omega$

• Optimal A =  $1\mu m^2$  for line lengths of 10mm

# Conclusion

- Constant impedance Scaling

- Systematic Approach to interconnect design

- Design strategies

- Applications

- Interconnect stack technology development

- On-chip global interconnects

- Package level interconnects

### Thank you

#### SEEDS FOR TOMORROW'S WORLD IMECNOLOGY

# **Backup Slides**

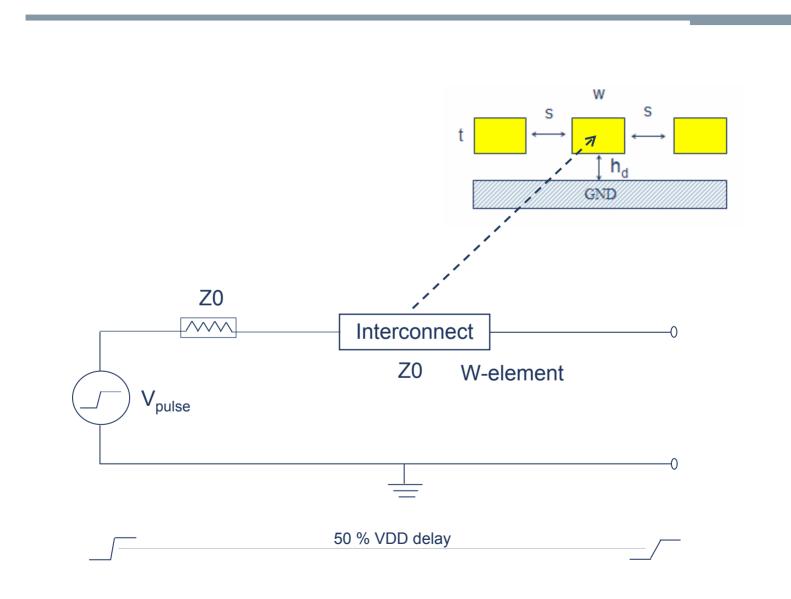

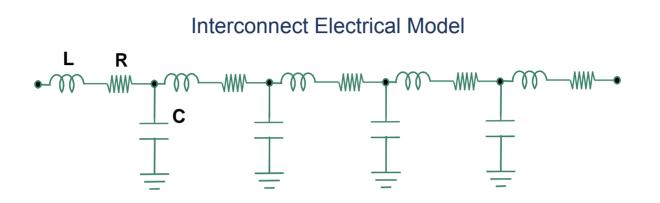

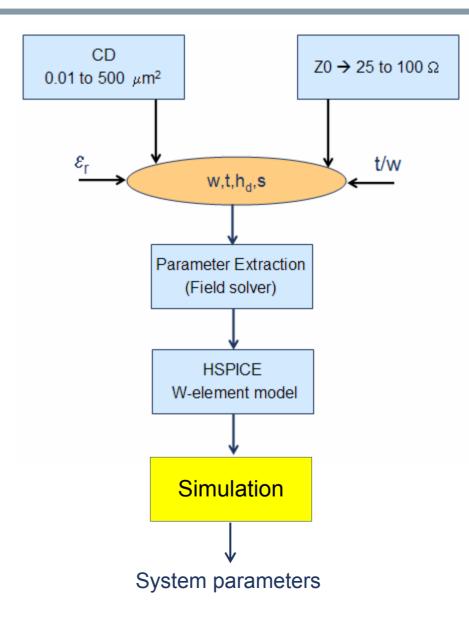

### **Interconnect Simulation Model**